40 Gigabit Ethernet (40GbE) iWARP RDMA, iSCSI, TOE, FCoE, NIC Engine

The Terminator 5 (T5) is Chelsio’s fifth generation ASIC. A highly integrated, hyper-virtualized 10Gb Ethernet (10GbE)/40Gb Ethernet (40GbE) controller, the Terminator 5 (T5) is built around a programmable protocol-processing engine, with full offload of a complete Unified Wire solution comprising NIC, TOE, iWARP RDMA, iSCSI, FCoE and NAT support. The Terminator 5 (T5) provides no-compromise performance with both low latency (1usec through hardware) and high bandwidth, limited only by the PCI bus. Furthermore, it scales true 40Gb line rate operation from a single TCP connection to thousands of connections, and allows simultaneous low latency and high bandwidth operation thanks to multiple physical channels through the ASIC.

Designed for high performance clustering, storage and data networks, the Terminator 5 (T5) enables fabric consolidation by simultaneously supporting wire-speed TCP/IP and UDP/IP socket applications, RDMA applications and SCSI applications, thereby allowing InfiniBand and FibreChannel applications to run unmodified over standard Ethernet. The API used for the complete software suite (on Linux, Windows and FSBD) for current Terminator 4 (T4) installations is the same for the Terminator 5 (T5) chip and future 100Gb capable versions, leveraging all the software investment that has been made in Terminator 4 (T4) deployments.

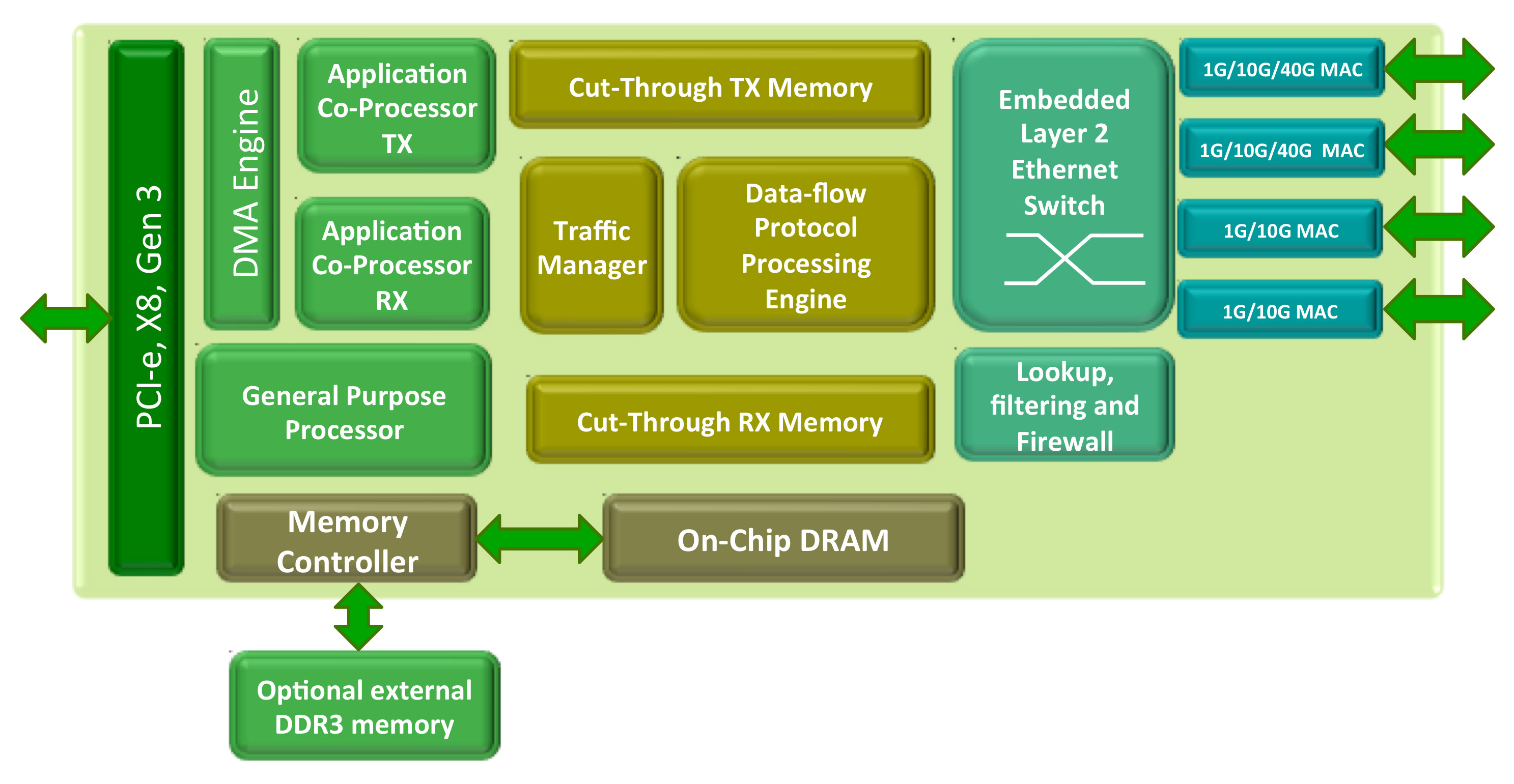

Chelsio Terminator 5 (T5) ASIC Architecture

The Terminator 5 (T5) ASIC is built around a highly scalable and programmable protocol-processing engine. In Terminator 5 (T5) much of the processing of the offloaded protocols is implemented in microcode running on a pipelined proprietary data-flow engine. The pipeline supports cut-through operation for both transmit and receive paths for minimum latency. The transport processor is designed for wire-speed operation at small packet sizes, regardless of the number of TCP connections.

Some key features of the Terminator 5 (T5):

- Integrated PCI Express v3.0 x8 host interface

- 2xDDR-3 memory interfaces

- 4x100M/1G/10G or 2x40G ports (40GbE)

- Designed for very low latency, highbandwidth and high packet processing rate

- NIC/TOE/iWARP RDMA/iSCSI/FCoE/NAT offload

- TOE/iWARP RDMA/iSCSI/FCoE port to port, and adapter to adapter failover

- SR-IOV 8PF/128VF + VEPA/VEB 802.1Qbg/h offload virtualization

- Integrated OpenFlow ready virtual Ethernet switch

- T10-DIF/DIX protection support for both FCoE and iSCSI

Related Articles:

Terminator 5 (T5) Architecture White Paper

Terminator 5 (T5) is a tightly integrated 4×10 Gigabi Ethernet (10GbE) / 2×40 Gigabit Ethernet (40GbE) controller chip built around a highly scalable and programmable protocol‐processing engine. In Terminator 5 (T5) much of the processing of the offloaded protocols is implemented in microcode running on a pipelined proprietary data-flow engine. The pipeline supports cut-through operation for both transmit and receive paths for minimum latency. The transport processor is designed for wire-speed operation at small packet sizes, regardless of the number of TCP connections. The Terminator 5 (T5) ASIC represents Chelsio’s fifth generation TCP offload (TOE) design, fourth generation iSCSI design, and third generation iWARP RDMA implementation. In addition to full TCP and iSCSI offload, T5 supports full FCoE offload. Terminator 5 (T5) supports failover between different ports of the Terminator 5 (T5) chip, as well as between different Terminator 5 (T5) adapters. Any TOE, iSCSI, or iWARP RDMA connection can fail over between different ports or between different adapters. Although the Terminator 5 (T5) pipeline is twice as fast as the Terminator 4 (T4) pipeline, the new chip can run the same microcode that has been field proven in very large clusters. Chelsio provides a uniform firmware interface across Terminator 4 (T4) and Terminator 5 (T5), and shields customers from the details of the Terminator hardware programming model.

Related Links:

Terminator 5 (T5) Product Brief

Download Software Drivers